# МИКРОСХЕМА ИНТЕГРАЛЬНАЯ 1892ВК016

РУКОВОДСТВО ПОЛЬЗОВАТЕЛЯ

РАЯЖ.431295.002Д17

#### ОГЛАВЛЕНИЕ

| 1. ВВЕДЕНИЕ                                                        | 10 |

|--------------------------------------------------------------------|----|

| 1.1 Назначение                                                     | 10 |

| 1.2 Функциональные параметры и возможности                         |    |

| 1.3 Структурная схема                                              |    |

| 1.4 Инструментальное программное обеспечение                       | 13 |

| 1.5 Операционная система для микросхемы 1892ВК016                  | 14 |

| 2. СИСТЕМНАЯ ОРГАНИЗАЦИЯ МИКРОСХЕМЫ                                | 15 |

| 2.1 Карта памяти                                                   | 15 |

| 2.2 Система синхронизации                                          |    |

| 2.2.1 Входы синхронизации и умножители частоты                     |    |

| 2.2.2 Управление работой PLL                                       |    |

| 2.2.3 Отключение и включение тактовой частоты                      |    |

| 2.3 Контроллер прерываний                                          | 29 |

| 2.4 Системные регистры                                             |    |

| 2.5 Процедура начальной загрузки                                   |    |

| 3. ПРОЦЕССОРЫ СРИ0, СРИ1                                           | 38 |

| 3.1 Основные характеристики                                        | 38 |

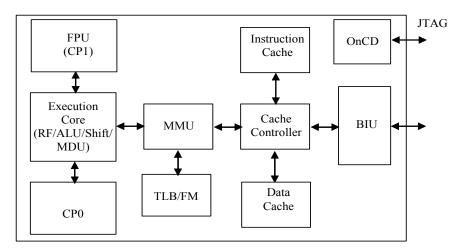

| 3.2 Блок-схема                                                     |    |

| 3.3 Составляющие логические блоки                                  |    |

| 3.3.1 Устройство исполнения                                        |    |

| 3.3.2 Устройство умножения/деления (MDU)                           |    |

| 3.3.3 Системный управляющий сопроцессор                            |    |

| 3.3.4 Устройство управления памятью (MMU)                          |    |

| 3.3.5 Контроллер кэш                                               |    |

| 3.3.6 Устройство шинного интерфейса (BIU – Bus Interface Unit)     | 40 |

| 3.3.7 OnCD контроллер                                              |    |

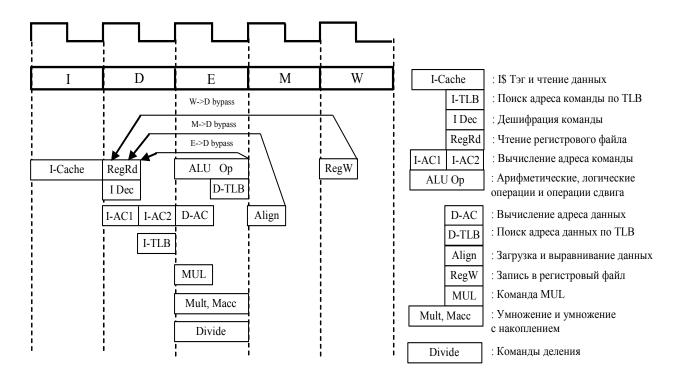

| 3.4 Конвейер                                                       | 41 |

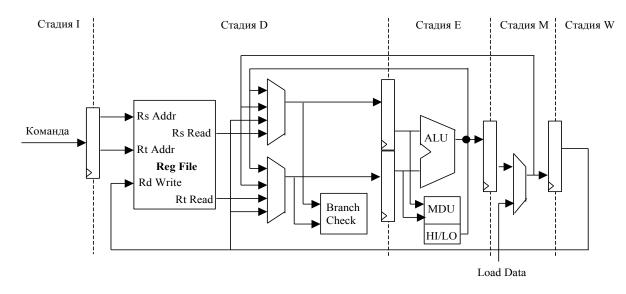

| 3.4.1 Стадии конвейера                                             | 41 |

| 3.4.2 Операции умножения и деления                                 | 43 |

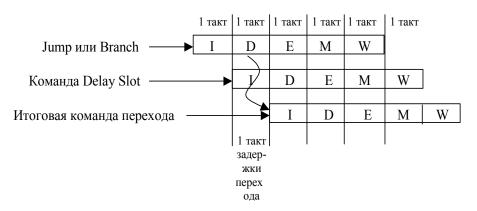

| 3.4.3 Задержка выполнения команд перехода (Jump, Branch)           | 43 |

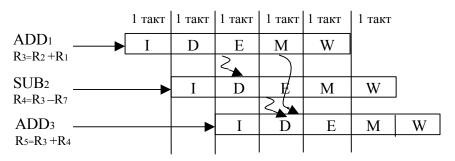

| 3.4.4 Обходные пути передачи данных (Data bypass)                  | 44 |

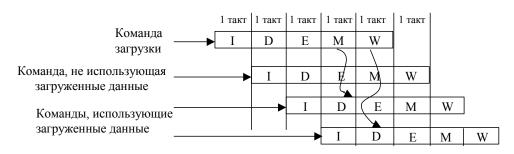

| 3.4.5 Задержка загрузки данных                                     | 45 |

| 3.5 Устройство управления памятью (MMU)                            |    |

| 3.5.1 Введение                                                     |    |

| 3.5.2 Режимы работы                                                |    |

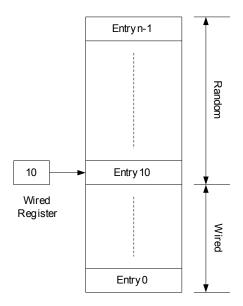

| 3.5.3 Буфер быстрого преобразования адреса (TLB)                   |    |

| 3.5.4 Преобразование виртуального адреса в физический в режиме TLB |    |

| 3.6 Исключения                                                     |    |

| 3.6.1 Условия исключений                                           |    |

| 3.6.2 Приоритеты исключений                                        |    |

| 3.6.3 Расположение векторов исключений                             | 62 |

| 3.6.4 Обработка общих исключений                                   |    |

| 3.6.5 Исключения                                                   |    |

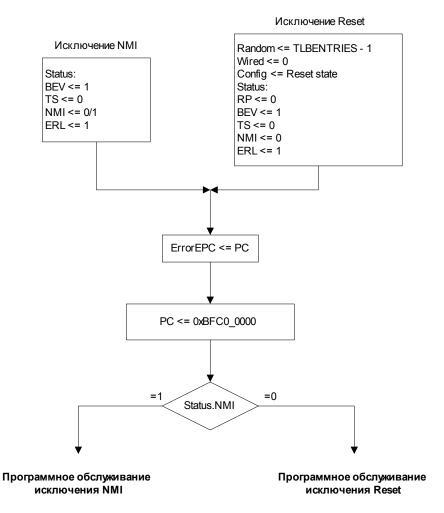

| 3.6.6 Алгоритмы обработки исключений                               |    |

| 3.7 Регистры СРО                                                   |    |

| 3.7.1 Назначение                                                   | 75 |

| 3.7.2 Обзор регистров СРО                        |     |

|--------------------------------------------------|-----|

| 3.7.3 Регистры СРО                               |     |

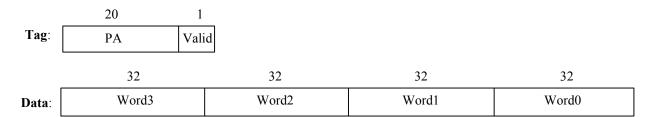

| 3.8 Кэш                                          | 94  |

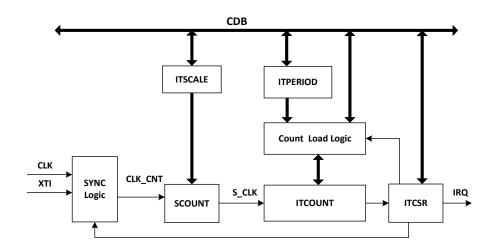

| 4. ИНТЕРВАЛЬНЫЙ ТАЙМЕР                           | 95  |

| 4.1 Назначение                                   | 95  |

| 4.2 Структурная схема IT                         |     |

| 4.3 Описание регистров интервального таймера     |     |

| 4.4 Программирование ІТ                          |     |

| 5. КОНТРОЛЛЕР ПРЯМОГО ДОСТУПА В ПАМЯТЬ (DMA)     | 98  |

| 5.1 Перечень каналов DMA                         | 98  |

| 5.2 Организация обмена данными в микросхеме      |     |

| 5.3 Каналы DMA типа память-память                |     |

| 5.4 Каналы DMA SWIC                              | 103 |

| 5.5 Процедура самоинициализации                  |     |

| 5.6 Прерывания DMA                               |     |

| 6. ПОРТ ВНЕШНЕЙ ПАМЯТИ ТИПА DDR SDRAM (DDR_PORT) | 108 |

| 6.1 Общие положения                              | 108 |

| 6.2 Регистры DDR PORT                            |     |

| 6.2.1 Регистр конфигурации DDRAM                 |     |

| 6.2.2 Регистр параметров DDR_TMR                 |     |

| 6.2.3 Регистр состояний и управления SDRCSR      |     |

| 6.2.4 Регистр режимов DDR_MOD                    |     |

| 6.2.5 Perистр DDR_EXT                            | 115 |

| 6.2.6 Регистр DDR_ERR                            | 116 |

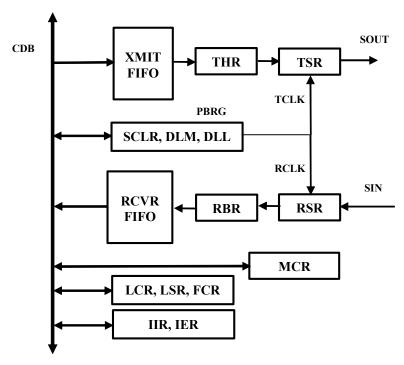

| 7. УНИВЕРСАЛЬНЫЙ АСИНХРОННЫЙ ПОРТ (UART)         | 118 |

| 7.1 Общие положения                              | 118 |

| 7.2 Регистры UART                                | 119 |

| 7.2.1 Общие положения                            | 119 |

| 7.2.2 Регистр LCR                                | 119 |

| 7.2.3 Регистр FCR                                | 120 |

| 7.2.4 Регистр LSR                                | 121 |

| 7.2.5 Регистр IER                                |     |

| 7.2.6 Регистр IIR                                |     |

| 7.2.7 Регистр MCR                                |     |

| 7.2.8 Программируемый генератор скорости обмена  |     |

| 7.3 Работа с FIFO по прерыванию                  |     |

| 7.4 Работа с FIFO по опросу                      | 126 |

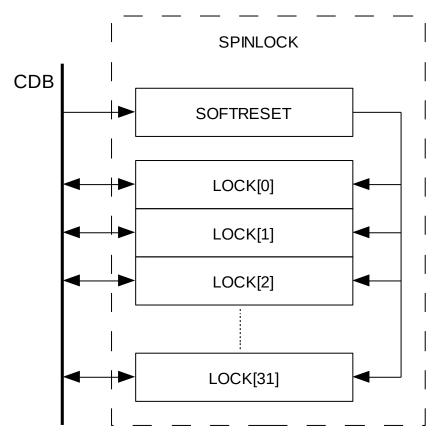

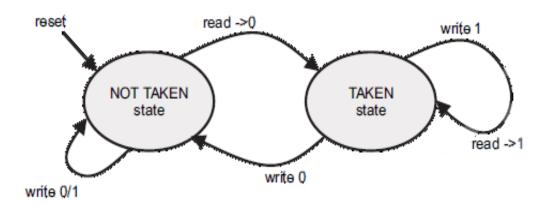

| 8. МОДУЛЬ SPINLOCK                               | 127 |

| 9. МОДУЛЬ ОБМЕНА СООБЩЕНИЯМИ MAILBOX             | 129 |

| 9.1 Назначение                                   |     |

| 9.2 Характеристики                               |     |

| 9.3 Регистры MAILBOX                             |     |

| 9.3.1 Регистр SOFT_RESET                         |     |

| 9.3.2 Регистр MESSAGE m                          |     |

| 9.3.3 Perucтр FIFO_STATUS_m                      |     |

|                                                  |     |

| 9.3.4 Регистры SET_IRQ_WRITE0, SET_IRQ_WRITE1           |     |

|---------------------------------------------------------|-----|

| 9.3.5 Регистры SET_IRQ_READ0, SET_IRQ_READ1             | 131 |

| 9.3.6 Регистры CLR_IRQ_WRITE0, CLR_IRQ_WRITE1           | 132 |

| 9.3.7 Регистры CLR_IRQ_READ0, CLR_IRQ_READ0             | 132 |

| 9.4 Методы организации межпроцессорного обмена данными  | 132 |

| 9.4.1 Обмен данными по прерыванию MAILBOX_READ          | 132 |

| 9.4.2 Обмен данными по прерыванию MAILBOX_WRITE         | 133 |

| 9.4.3 Обмен данными по опросу                           | 133 |

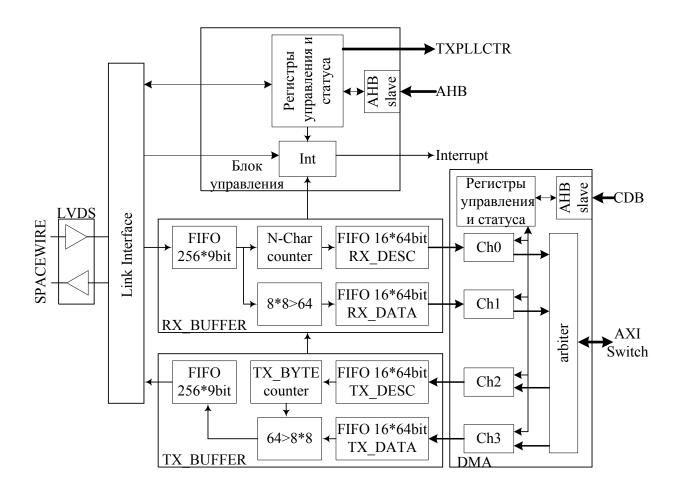

| 10. КОНТРОЛЛЕР ИНТЕРФЕЙСА SPACEWIRE (SWIC)              | 134 |

|                                                         |     |

| 10.1 Общие положения                                    |     |

| 10.2 Блок схема                                         |     |

| 10.3 Прерывания                                         |     |

| 10.4 Перечень регистров SWIC                            |     |

| 10.4.1 Общие положения                                  |     |

| 10.5 Описание регистров SWIC                            |     |

| 10.5.1 Perистр HW_VER                                   |     |

| 10.5.2 Perucтр STATUS                                   |     |

| 10.5.3 Perucтр RX_CODE                                  |     |

| 10.5.4 Peгистр MODE_CR                                  |     |

| 10.5.5 Peгистр TX_SPEED                                 |     |

| 10.5.6 Регистр RX_SPEED                                 |     |

| 10.5.7 Регистр ТХ_CODE                                  |     |

| 10.5.8 Регистр CNT_RX_PACK                              |     |

| 10.5.9 Регистр CNT_RX0_PACK                             | 146 |

| 10.5.10 Регистр ISR_L                                   | 146 |

| 10.5.11 Регистр ISR_H                                   | 147 |

| 10.5.12 Perистр TRUE_TIME                               | 147 |

| 10.5.13 Perucтр TOUT CODE                               | 147 |

| 10.5.14 Perистр ISR tout L                              | 148 |

| 10.5.15 Perистр ISR tout H.                             | 148 |

| 10.5.16 Регистр LOG ADDR                                | 148 |

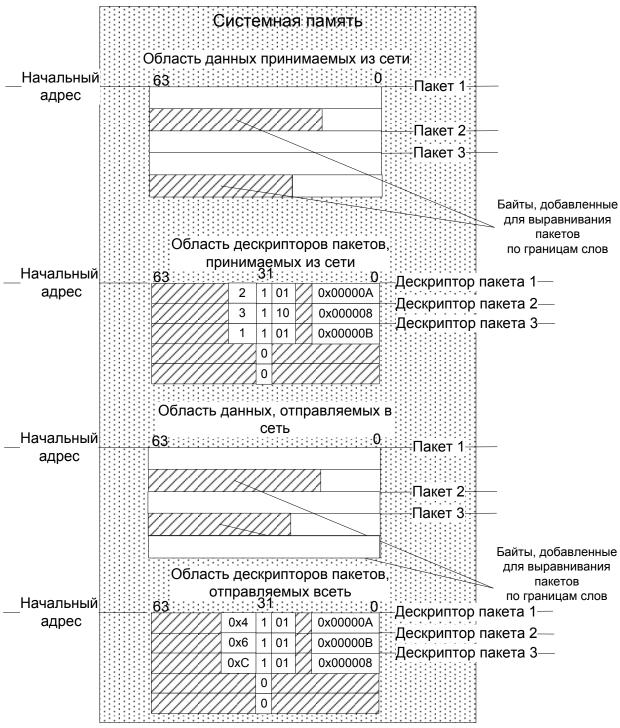

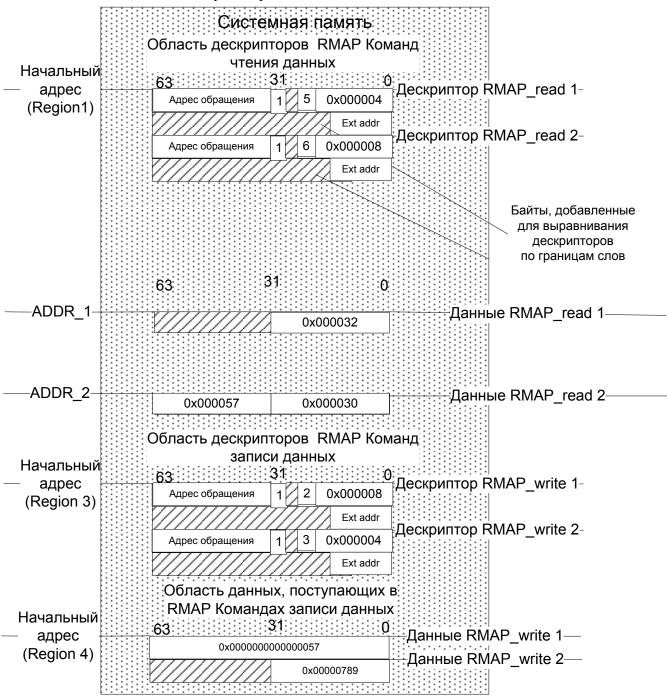

| 10.6 Работа со SWIC. Пакеты данных, дескрипторы пакетов |     |

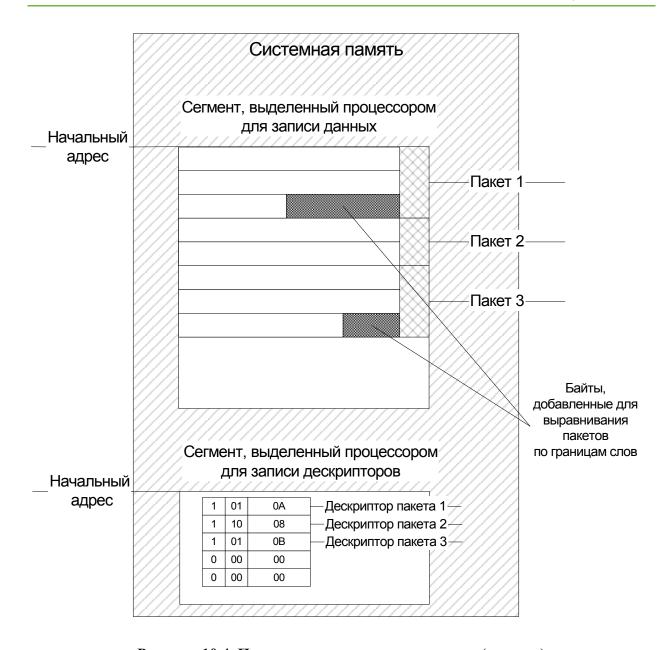

| 10.6.1 Расположение данных в памяти                     |     |

| 10.6.2 Схема обработки данных процессором               |     |

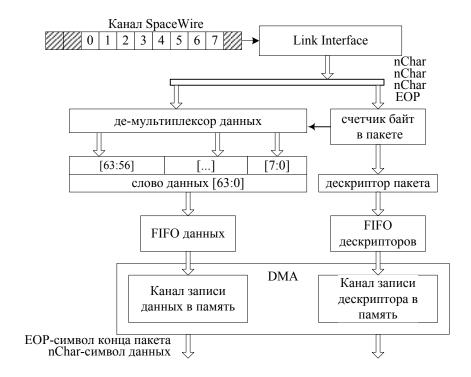

| 10.6.3 Прием данных из канала SpaceWire.                |     |

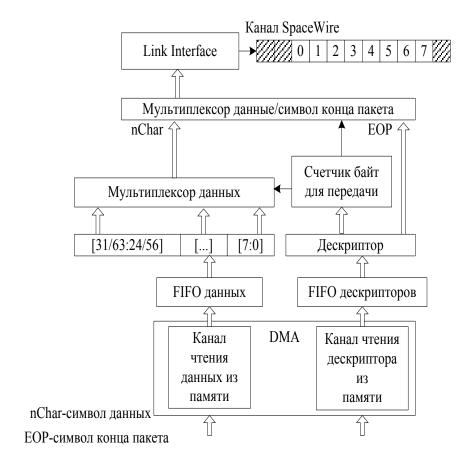

| 10.6.4 Передача данных в канал SpaceWire                |     |

| 10.6.5 Выравнивание границ пакетов по границам слов     |     |

| 10.6.6 Формат дескриптора пакета                        |     |

| 10.6.7 Возможность передачи коммуникационного пакета    |     |

| 10.6.8 Использование симплексного режима                |     |

| 10.6.9 Маркеры времени                                  |     |

| 10.6.10 Коды распределенных прерываний                  | 157 |

| 10.6.11 Коды подтверждения распределенных прерываний    |     |

| 10.6.12 Установка скорости передачи данных              |     |

| 10.6.13 Установка екорости переда и данных              |     |

| 10.6.14 Определение скорости приема данных              |     |

|                                                         |     |

| 11. KOMMYTATOP SPFR                                     |     |

| 11.1 Функциональные параметры и возможности             |     |

| 11.2 Типы информационных потоков                        | 160 |

| 11.2.1 Введение                                                        | 60  |

|------------------------------------------------------------------------|-----|

| 11.2.2 Потоки пакетов транспортных протоколов с частичной обработкой в |     |

| SpFR1                                                                  |     |

| 11.2.3 Потоки пакетов SpW без обработки в коммутаторе SpFR             |     |

| 11.2.4 Потоки пакетов в пространство конфигурации коммутатора SpFR 1   |     |

| 11.3 Перечень программно-доступных регистров коммутатора SpFR          |     |

| 11.4 Описание программно-доступных регистров                           |     |

| 11.4.1 Регистр ID_VER 1                                                |     |

| 11.4.2 Perucтр ID SWITCH                                               |     |

| 11.4.3 Perucтр DMA_CHANNELS_MODE 1                                     | 69  |

| 11.4.4 Perucтр DMA_CHANNELS_WORK_EN 1                                  |     |

| 11.4.5 Perucтр DMA_RMAP_CONFIGURATION 1                                |     |

| 11.4.6 Perucтр DMA REGIONS 12 STATUS                                   |     |

| 11.4.7 Perucтр DMA REGIONS 34 STATUS                                   | 74  |

| 11.4.8 Регистр DMA_PACK_STATUS                                         | 74  |

| 11.4.9 Perucтр DMA IRQ MASK 1                                          | 75  |

| 11.4.10 Регистр DMA_IRQ_MASK21                                         | 76  |

| 11.4.11 Регистр DMA_IRQ_MASK3 1                                        | 76  |

| 11.4.12 Регистр DMA START ADDR R1                                      |     |

| 11.4.13 Регистр DMA AREA SIZE R11                                      |     |

| 11.4.14 Регистр DMA START ADDR R2                                      |     |

| 11.4.15 Регистр DMA AREA SIZE R2                                       |     |

| 11.4.16 Регистр DMA_START_ADDR_R31                                     |     |

| 11.4.17 Регистр DMA AREA SIZE R3                                       |     |

| 11.4.18 Регистр DMA START ADDR R4                                      |     |

| 11.4.19 Регистр DMA_AREA_SIZE_R4                                       |     |

| 11.4.20 Регистр FIFO ANS                                               |     |

| 11.4.21 Perucтр FIFO_STATUS                                            | 80  |

| 11.4.22 Регистр REJ STATUS                                             | 81  |

| 11.4.23 Perucтр RMAP_REC_PACK_COUNTERS_1 1                             |     |

| 11.4.24 Perистр RMAP_REC_PACK_COUNTERS_21                              |     |

| 11.4.25 Регистр ID NET 1                                               |     |

| 11.4.26 Регистр MODE_R 1                                               | 85  |

| 11.4.27 Peгистр MODE_R1 1                                              |     |

| 11.4.28 Регистр STATE_R1                                               | 86  |

| 11.4.29 Perucтр STATE_R_CONNECT                                        | .87 |

| 11.4.30 Perucтр STATE_R_ERROR                                          |     |

| 11.4.31 Регистр IRQ_MASK1                                              | 88  |

| 11.4.32 Регистр GiGA_SPW_STATUS                                        | 90  |

| 11.4.33 Регистр GIGA SPW MODE                                          |     |

| 11.4.34 Регистр GIGA_SPW_TRANSMISSION_PARAMETERS 1                     | .91 |

| 11.4.35 Регистр GIGA_SPW_CREDIT_PARAMETERS 1                           | .92 |

| 11.4.36 Регистр РМА_STATUS                                             |     |

| 11.4.37 Регистр РМА_MODE 1                                             | 93  |

| 11.4.38 Peгистр SpF_PORT_MODE_VC_PARAMS 1                              |     |

| 11.4.39 Регистр SpF_PORT_MODE_VC_TSLOTS_L                              |     |

| 11.4.40 Peгистр SpF_PORT_MODE_VC_TSLOTS_H 1                            | 95  |

| 11.4.41 Peгистр SpF_PORT_MODE_VC_FR_LL 1                               |     |

| 11.4.42 Peгистр SpF_PORT_MODE_LANE_CONSTANTS 1                         |     |

| 11.4.43 Peгистр SpF_PORT_STATUS_VC11                                   |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 19/                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 11.4.45 Peгистр SpF_PORT_CUR_CREDIT_VALUE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 198                                                                                                                                               |

| 11.4.46 Регистр SpF_PORT_STATUS_LL_EL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 198                                                                                                                                               |

| 11.4.47 Регистр ADG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 199                                                                                                                                               |

| 11.4.48 Peгистр CHANNEL_ROUTING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 199                                                                                                                                               |

| 11.4.49 Peгистр CHANNEL_REGISTERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 200                                                                                                                                               |

| 11.4.50 Регистр DRT_TOUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 200                                                                                                                                               |

| 11.4.51 Регистр DRT_TOUTS_VALIDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 201                                                                                                                                               |

| 11.4.52 Peгистр DRT_TOUTS_FLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 201                                                                                                                                               |

| 11.4.53 Регистр DA_TOUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 201                                                                                                                                               |

| 11.4.54 Регистр DA_SPF_TOUTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 202                                                                                                                                               |

| 11.4.55 Регистр DA_SPF_TOUTS2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                   |

| 11.4.56 Регистр DA_SPF_TOUTS_FLS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 203                                                                                                                                               |

| 11.4.57 Регистр INCORRECT_VC_INFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 204                                                                                                                                               |

| 11.4.58 Регистр SPEC_VC_ARB_PARAMETERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                   |

| 11.4.59 Регистр SPEC_ARB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 205                                                                                                                                               |

| 11.4.60 Регистр CONTROL_CONNECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                   |

| 11.5 Описание логики работы контроллеров транспортного уровня, DMA комм                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | иутатора                                                                                                                                          |

| 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                   |

| 11.6 Конфигурирование областей памяти для виртуальных каналов, предназна                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |

| для обращений в пространство конфигурации или команд SpW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |

| 11.7 Конфигурирование областей памяти для виртуальных каналов, предназна                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                   |

| для обработки пакетов Транспортных протоколов                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                   |

| 11.8 Перечень прерываний, формируемых коммутатором SpFR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 218                                                                                                                                               |

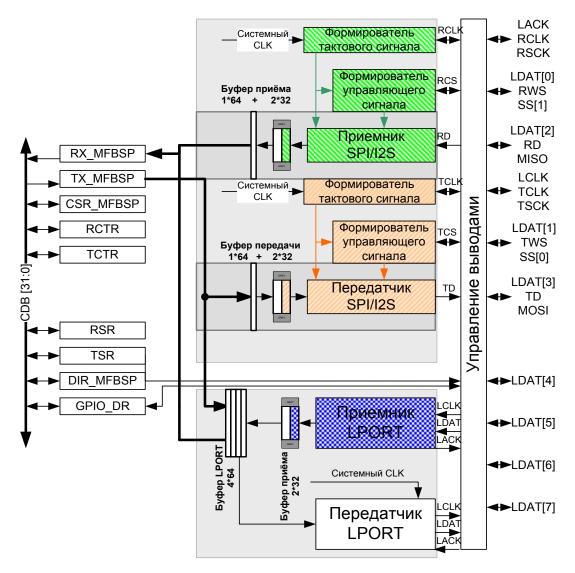

| 12. МНОГОФУНКЦИОНАЛЬНЫЙ БУФЕРИЗИРОВАНННЫЙ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 226                                                                                                                                               |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                   |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 226                                                                                                                                               |

| <b>ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)</b> 12.1 Общие сведения об MFBSP 12.1.1 Режимы работы MFBSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 226<br>226                                                                                                                                        |

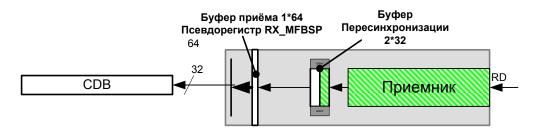

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 226<br>226<br>эванного                                                                                                                            |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 226<br>226<br>эванного<br>227                                                                                                                     |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 226<br>226<br>эванного<br>227<br>228                                                                                                              |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 226<br>226<br>ованного<br>227<br>228<br>229                                                                                                       |

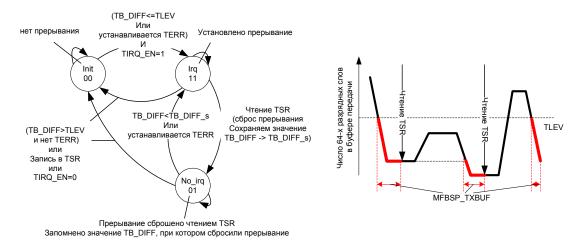

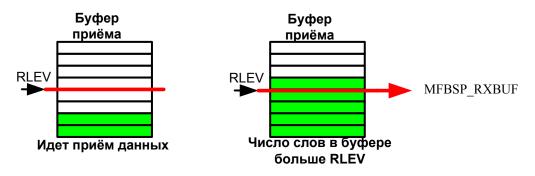

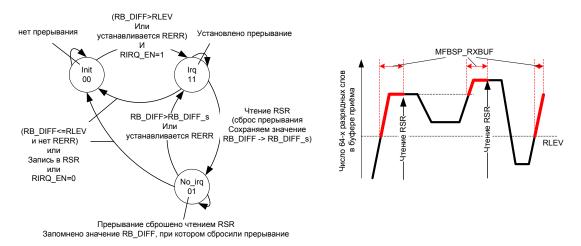

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 226<br>226<br>ованного<br>227<br>228<br>229<br>230                                                                                                |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232                                                                                         |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232                                                                                         |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233                                                                           |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)                                                                                                                                                                                                                                                                                                                                                                                               | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234                                                                    |

| 12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)                                                                                                                                                                                                                                                                                                                                                                       | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234<br>235                                                             |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления передатчиком TCTR (режим SPI)                                                                                                                                                                                                                                                                               | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234<br>235<br>237                                                      |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2.1 Назначение последовательного порта в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления передатчиком TCTR (режим SPI)  12.2.6 Регистр состояния приёмника RSR (режим SPI)                                                                                                                                                                                                   | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234<br>235<br>237<br>239                                               |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления передатчиком TCTR (режим SPI)  12.2.6 Регистр состояния приёмника RSR (режим SPI)  12.2.7 Регистр состояния передатчика TSR (режим SPI)                                                                                                                                                                     | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234<br>235<br>237<br>239<br>240                                        |

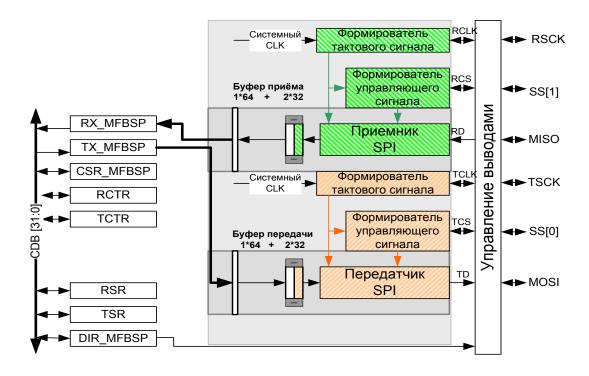

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления приёмником TCTR (режим SPI)  12.2.6 Регистр состояния приёмника RSR (режим SPI)  12.2.7 Регистр состояния приёмника RSR (режим SPI)  12.2.8 Структурная схема MFBSP для режима SPI                                                                                                                          | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234<br>235<br>237<br>239<br>240                                        |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2. Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления передатчиком TCTR (режим SPI)  12.2.6 Регистр состояния приёмника RSR (режим SPI)  12.2.7 Регистр состояния передатчика TSR (режим SPI)  12.2.8 Структурная схема MFBSP для режима SPI  12.2.9 Соединение порта с внешним устройством                                                                      | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234<br>235<br>237<br>239<br>240<br>241                                 |

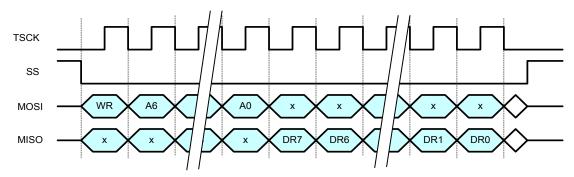

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2. Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления передатчиком TCTR (режим SPI)  12.2.6 Регистр состояния приёмника RSR (режим SPI)  12.2.7 Регистр состояния передатчика TSR (режим SPI)  12.2.8 Структурная схема MFBSP для режима SPI  12.2.9 Соединение порта с внешним устройством  12.2.10 Передача данных в режиме SPI                                | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>233<br>234<br>235<br>237<br>239<br>240<br>241<br>242                                 |

| 12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2 Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления приёмником TCTR (режим SPI)  12.2.6 Регистр состояния приёмника RSR (режим SPI)  12.2.7 Регистр состояния приёмника RSR (режим SPI)  12.2.8 Структурная схема MFBSP для режима SPI  12.2.9 Соединение порта с внешним устройством  12.2.10 Передача данных в режиме SPI  12.2.11 Пример чтения 8 разрядного слова по заданному адресу из в | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>233<br>234<br>235<br>237<br>239<br>240<br>241<br>242<br>eдомого                      |

| ПОСЛЕДОВАТЕЛЬНЫЙ ПОРТ (MFBSP)  12.1 Общие сведения об MFBSP  12.1.1 Режимы работы MFBSP  12.1.2 Структурная схема многофункционального буферизиро последовательного порта  12.1.3 Назначение выводов порта в различных режимах  12.1.4 Перечень регистров MFBSP  12.1.5 Прерывания от MFBSP  12.2. Работа MFBSP в режиме SPI  12.2.1 Назначение последовательного порта в режиме SPI  12.2.2 Регистр управления и состояния CSR_MFBSP (режим SPI)  12.2.3 Регистр управления направлением выводов DIR_MFBSP (режим SPI)  12.2.4 Регистр управления приёмником RCTR (режим SPI)  12.2.5 Регистр управления передатчиком TCTR (режим SPI)  12.2.6 Регистр состояния приёмника RSR (режим SPI)  12.2.7 Регистр состояния передатчика TSR (режим SPI)  12.2.8 Структурная схема MFBSP для режима SPI  12.2.9 Соединение порта с внешним устройством  12.2.10 Передача данных в режиме SPI                                | 226<br>226<br>ованного<br>227<br>228<br>229<br>230<br>232<br>232<br>233<br>234<br>235<br>237<br>239<br>240<br>241<br>242<br>242<br>едомого<br>244 |

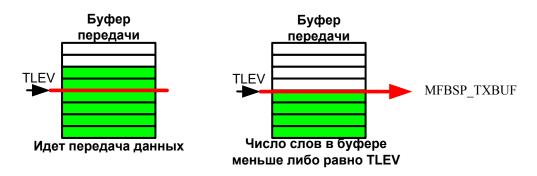

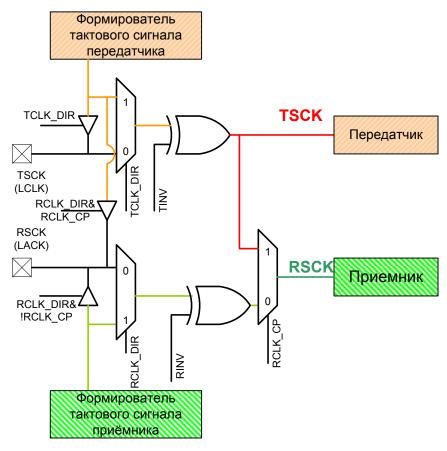

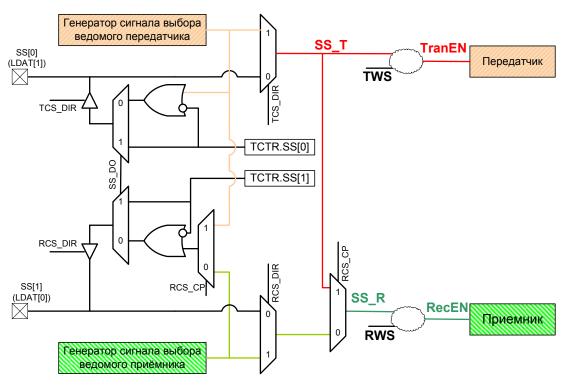

| 12.2.13 Формирование управляющих сигналов приемника и передатчик | •   |

|------------------------------------------------------------------|-----|

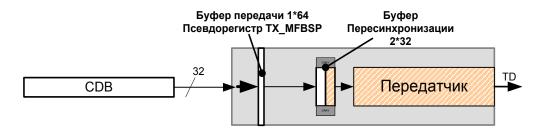

| 12.2.14 Тракт передачи данных                                    |     |

| 12.2.15 Тракт приёма данных                                      |     |

| 12.2.16 Прерывания от последовательного порта                    |     |

| 12.3 Работа MFBSP в режиме порта ввода-вывода общего назначения  |     |

| 12.3.1 Регистр данных порта ввода вывода GPIO_DR                 |     |

| 12.3.2 Регистр управления направлением выводов DIR_MFBSP         | 252 |

| 13. NAND FLASH CONTROLLER                                        | 254 |

| 13.1 Общие положения                                             | 254 |

| 13.1.1 Функциональные параметры и возможности                    | 254 |

| 13.1.2 Cостав NFC                                                | 255 |

| 13.1.3 Термины и определения                                     | 255 |

| 13.2 Регистры NFC                                                |     |

| 13.2.1 Перечень регистров NFC                                    |     |

| 13.2.2 Регистр РАСКЕТ                                            | 258 |

| 13.2.3 Регистр MEMADDR1                                          |     |

| 13.2.4 Регистр MEMADDR2                                          |     |

| 13.2.5 Регистр COMMAND.                                          |     |

| 13.2.6 Регистр PROGRAM                                           |     |

| 13.2.7 Perucтр INTERRUPT_STATUS_EN                               |     |

| 13.2.8 Регистр INTERRUPT_SIGNAL_EN                               | 267 |

| 13.2.9 Регистр INTERRUPT_STATUS                                  |     |

| 13.2.10 Регистр ID1                                              |     |

| 13.2.11 Регистр ID2                                              |     |

| 13.2.12 Perucтр FLASH_STATUS                                     |     |

| 13.2.13 Peructp TIMING                                           |     |

| 13.2.14 Perистр BUFFER_DATA                                      |     |

| 13.2.15 Peructp ECC                                              |     |

| 13.2.16 Peructp ECC_ERROR_CNT                                    |     |

| 13.2.17 Peructp ECC_SPARE_CMD.                                   |     |

| 13.2.18 Perистры ERROR_CNT_nBIT                                  |     |

| 13.2.19 Peructp DMA_ADDR                                         |     |

| 13.2.20 Peructp DMA_BUFFER_BOUNDARY                              |     |

| 13.2.21 Peructp WRITE_PROTECT                                    |     |

| 13.3 Описание выполнения операций с флэш-памятью                 |     |

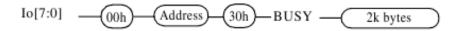

| 13.3.1 Схема выполнения команды «Без доступа к FIFO»             |     |

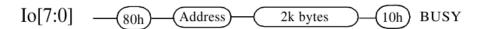

| 13.3.2 Схема выполнения команды «С чтением из FIFO»              |     |

| 13.3.3 Схема выполнения команды «С записью в FIFO»               |     |

| 13.3.4 Команда Reset                                             |     |

|                                                                  |     |

| 13.3.6 Команда Read ID                                           |     |

| 13.3.7 Команда Read Parameter Page                               |     |

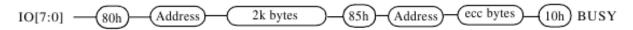

| 13.3.9 Команда Page Program с ECC                                |     |

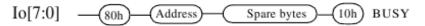

| 13.3.10 Команда Раде Program для spare области                   |     |

| 13.3.11 Команда Page Program для spare области                   |     |

| 13.3.12 Команда Read c ECC                                       |     |

| 13.3.13 Команда Read для spare области                           |     |

| 10.0.10 Itomaniqu Itoma gain upuro uvauerin                      |     |

|     | 13.3.14 Команда Block Erase                               | 288 |

|-----|-----------------------------------------------------------|-----|

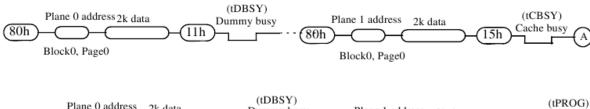

|     | 13.3.15 Команда Multi-plane Page Program                  | 288 |

|     | 13.3.16 Команды Multi-plane Copyback                      | 289 |

|     | 13.3.17 Команда Multi-plane Block Erase                   | 290 |

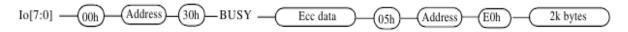

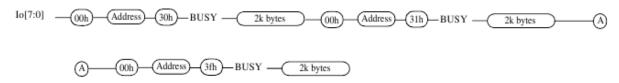

|     | 13.3.18 Команда Multi-plane Read                          | 291 |

|     | 13.3.19 Команда Multi-plane Read с ECC                    | 292 |

|     | 13.3.20 Команда Page Cache Program (2 interleaved адреса) | 294 |

|     | 13.3.21 Команда Page Cache Program                        |     |

|     | 13.3.22 Команда Read Cashe Sequential                     |     |

|     | 13.3.23 Команда Read Cashe Random                         |     |

|     | 13.3.24 Выбор LUN/die                                     |     |

|     | 13.3.25 Команда Read Status Enhanced                      |     |

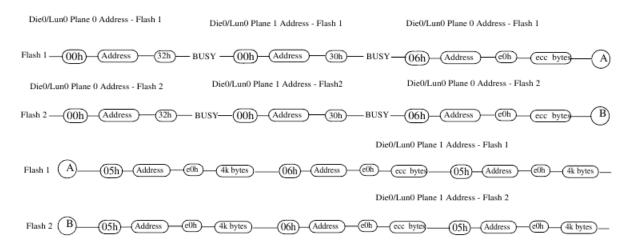

|     | 13.3.26 Page Program LUN0, Page Program LUN1              |     |

|     | 13.3.27 Read LUN0, Read LUN1                              |     |

|     | 13.3.28 Block Erase LUN0, Block Erase LUN1                |     |

|     | 13.3.29 Page Program LUN0, Read LUN1                      |     |

|     | 13.3.30 Small Data Move                                   |     |

|     | 13.3.31 Small Data Move, Page Program                     |     |

|     | 13.3.32 Small Data Move, Copyback Program                 |     |

|     | 13.3.33 Small Data Move, Change Read Column Enhanced      |     |

|     | 13.3.34 Команда Change Row Address                        |     |

|     | 13.3.35 Команда Change Row Address                        |     |

|     | 13.3.36 Свойство Page Register Clear Enhancement          |     |

|     | 13.3.37 Команда Set Features                              |     |

|     | 13.3.38 Команда Get Features                              |     |

|     | 13.3.39 Переключение временных режимов                    |     |

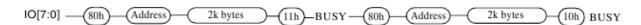

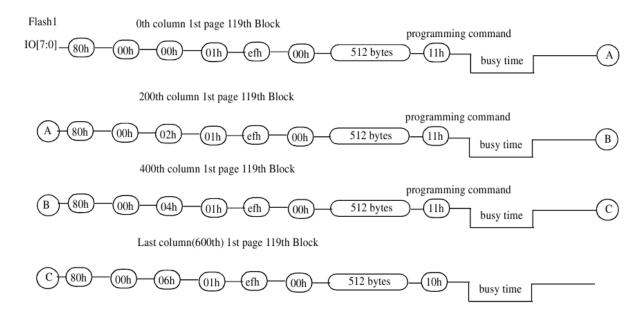

|     | 13.3.40 Page Program (режим MDMA)                         |     |

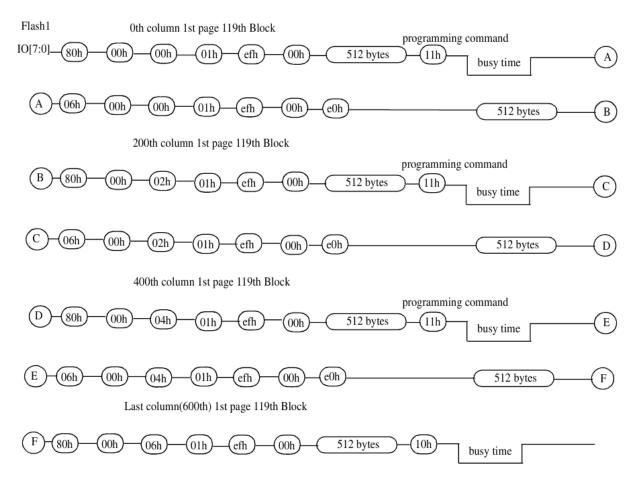

|     | 13.3.41 Read (режим MDMA)                                 |     |

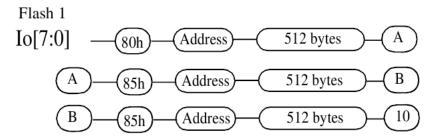

|     | .4 Обнаружение и инициализация флэш-памяти                |     |

|     | .5 Настройка тактирования NFC                             |     |

|     | .6 Прерывания                                             |     |

|     | .7 Подключение NAND флэш-памяти                           |     |

|     | 13.7.1 Последовательный способ работы                     |     |

|     | 13.7.2 Параллельный способ работы                         |     |

|     |                                                           |     |

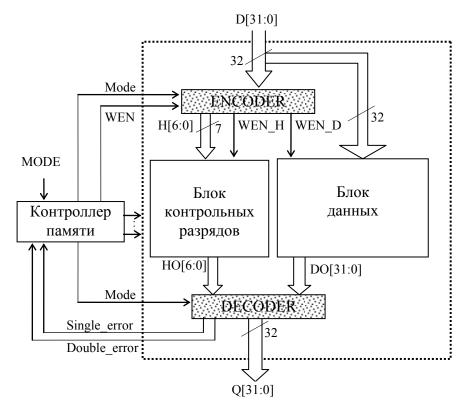

| 14. | ПРИНЦИПЫ КОРРЕКЦИИ ОШИБОК                                 | 311 |

| 15. | ПОРТ ЈТАС И ВСТРОЕННЫЕ СРЕДСТВА ОТЛАДКИ ПРОГРАММ          | 315 |

| 16. | ЭЛЕКТРИЧЕСКИЕ И ВРЕМЕННЫЕ ПАРАМЕТРЫ                       | 316 |

| 16  | .1 Электропитание                                         | 316 |

| 16  | .2 Электрические параметры                                | 317 |

|     | .3 Динамическая потребляемая мощность                     |     |

| 17. | ОПИСАНИЕ ВНЕШНИХ ВЫВОДОВ                                  |     |

| 18. | ИСТОРИЯ ИЗМЕНЕНИЙ                                         | 330 |

| 12  | .1 25 мая 2017 г                                          |     |

|     | .2 20 ноября 2017 г                                       |     |

|     | .3 29 января 2018 г                                       |     |

|     | .4 15 марта 2018 г                                        |     |

| 10  | . 1 10 Mapta 2010 1                                       | 551 |

| 18.5 18 декабря 2018 г  | 3. | 3 |

|-------------------------|----|---|

| 18.6 16 сентября 2019 г | 3. | 3 |

## 1. ВВЕДЕНИЕ

#### 1.1 Назначение

Микросхема интегральная контроллера сетевого твердотельного накопителя информации 1892ВК016 (МСТ-04) спроектирована как однокристальная «система на кристалле» на базе IP-ядерной (IP-intellectual property) платформы «МУЛЬТИКОР», разработанной в АО НПЦ «ЭЛВИС».

Микросхема 1892ВК016 предназначена для применения в бортовых твердотельных накопителях информации объемом до 1 терабайта.

#### 1.2 Функциональные параметры и возможности

Микросхема 1892ВК016 имеет следующие функциональные параметры и возможности:

- два центральных процессора (CPU0. CPU1):

- архитектура MIPS32;

- 32-х битные шины передачи адреса и данных;

- кэш команд объемом 32 Кбайт;

- кэш данных объемом 32 Кбайт;

- архитектура привилегированных ресурсов в стиле ядра R4000:

- о регистры Count/Compare для прерываний реального времени;

- о отдельный вектор обработки исключений по прерываниям;

- программируемое устройство управления памятью:

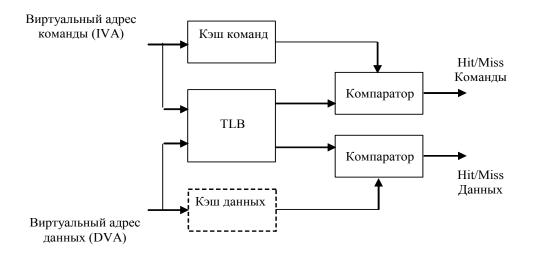

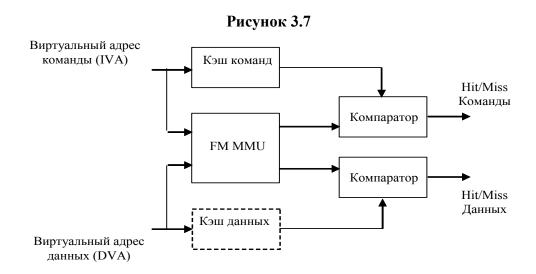

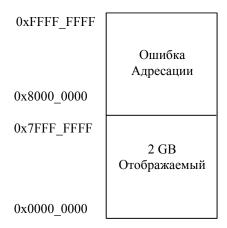

- два режима работы с TLB (Translation Lookaside Buffer) и FM (Fixed Mapped);

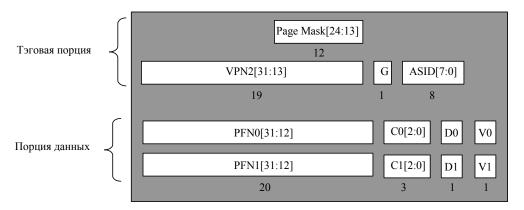

- о 16 строк в режиме TLB;

- устройство умножения и деления;

- JTAG IEEE 1149.1, встроенные средства отладки программ;

- оперативная память центрального процессора (CRAM) объемом 128 Кбайт;

- 1 внешний запрос прерывания;

- порт внешней памяти типа DDR (DDR PORT):

- шина данных 32 разряда;

- пиковая пропускная способность 1600 Мбайт/с;

- программное конфигурирование типа блоков памяти и их объема;

- перевод DDR SDRAM в режим энергосбережения;

- периферийные устройства:

- два дуплексных порта по стандарту SpaceWire (ECSS-E-50-12C) с пропускной способностью от 2 до 300 Мбод каждый (SWIC0, SWIC1).

Порты подключены к коммутатору АХІ через 8-канальный контроллер DMA;

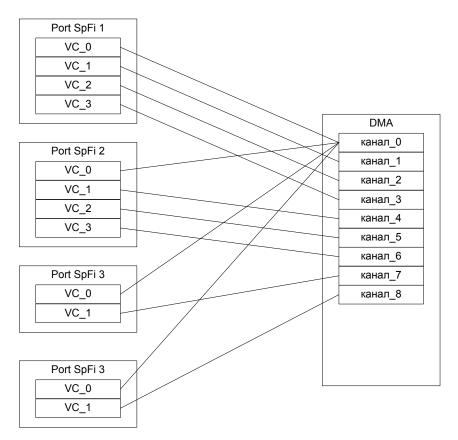

- 4-портовый мультипротокольный коммутатор SpaceFibre/GigaSpaceWire (SpaceWire-RUS). Пропускная способность каждого порта от 5 Мбод до 1,25 Гбод. Поддерживает протокол RMAP. Коммутатор подключен к коммутатору АХІ через два многоканальных контроллера DMA;

- 8 портов NFC со встроенным каналом DMA для подключения ONFI 2 NAND Flash. Каждый порт обеспечивает подключение до 16 8-разрядных микросхем NAND Flash;

- многофункциональный буферизированный последовательный порт (MFBSP) работающий в режимах контроллера шины SPI и порта ввода-вывода общего назначения GPIO[2:0];

- 8-канальный контроллер прямого доступа (DMA) типа память-память;

- контроллер прерываний;

- универсальный асинхронный порт (UART) типа 16550;

- два универсальных 32-разрядных таймера (IRT0, IRT1), интервальные/реального времени с двумя источниками входной частоты: CLK, XTI;

- дополнительные возможности и особенности:

- умножители/делители входной частоты на основе узлов фазовой автоподстройки частоты (PLL);

- коррекция ошибок внутренней и внешней памяти: исправление однократных ошибок и обнаружение двукратных ошибок по коду Хэмминга;

- встроенные средства отладки программ (OnCD) с портом JTAG в соответствии со стандартом IEEE 1149.1;

- режимы энергосбережения;

- поддержка операционной системы Linux;

- керамический корпус типа CPGA-720.

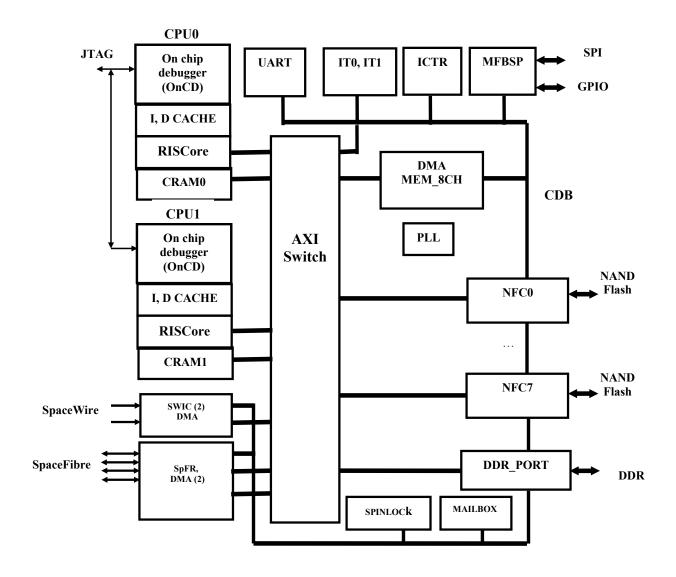

#### 1.3 Структурная схема

Структурная схема микросхемы 1892ВК016 приведена на рисунке 1.1.

Рисунок 1.1. Структурная схема микропроцессора 1892ВК016

В состав микросхемы 1892ВК016 входят следующие основные узлы:

- CPU0, CPU1 центральные процессоры 0, 1 на основе RISC-ядер;

- I, D CACHE кэш команд и кэш данных CPU;

- CRAM0, CRAM1 оперативная память процессоров;

- CDB шина данных CPU;

- DMA MEM CH 8-канальный контроллер прямого доступа типа память-память;

- DDR PORT порт внешней памяти типа DDR;

- NFC0:NFC7 контроллер внешней памяти типа NAND Flash (NAND FLASH CONTROLLER);

- DMA контроллер прямого доступа в память;

- SPINLOCK модуль низкоуровневого взаимоисключающего примитива синхронизации;

- MAILBOX модуль обмена сообщениями;

- OnCD встроенные средства отладки программ;

- AXI Switch коммутатор AXI;

- PLL умножители частоты на основе PLL;

- SWIC0, SWIC1 контроллеры интерфейса SpaceWire;

- SpFR (SpaceFibre Router) 4-портовый мультипротокольный коммутатор SpaceFibre/GigaSpaceWire (SpaceWire-RUS). Поддерживает протокол RMAP. Подключен к коммутатору АХІ через два многоканальных контроллера DMA;

- MFBSP многофункциональный буферизированный последовательный порт работающий в режимах контроллера шины SPI и GPIO[2:0];

- ICTR контроллер прерываний;

- UART универсальный асинхронный порт;

- IRT0, IRT1 универсальные таймеры, интервальные/реального времени;

- JTAG отладочный порт.

Коммутатор обеспечивает передачу данных между любым исполнительным устройством (Slave) и любым задатчиком (Master). При этом процесс передачи данных между любыми парами Slave

Маster выполняется параллельно и без конфликтов.

Исполнительными устройствами являются блоки внутренней памяти CRAM или внешняя память, доступная через DDR\_PORT. Задатчиками могут быть CPU, каналы DMA SWIC, SpFR, NFC, каналы DMA типа память-память.

# 1.4 Инструментальное программное обеспечение

Для данной микросхемы разработана интегрированная среда проектирования программного обеспечения MCStudio, которая обеспечивает полный цикл разработки и отладки программ. Эта среда функционирует на инструментальной машине IBM PC в среде Windows.

Интегрированная среда проектирования включает:

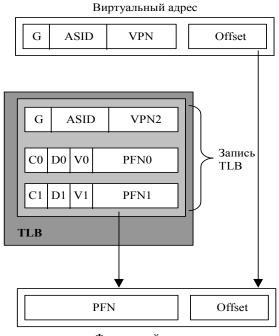

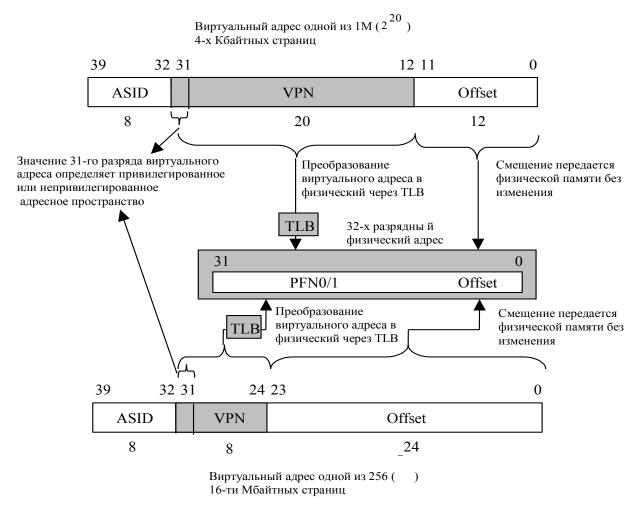

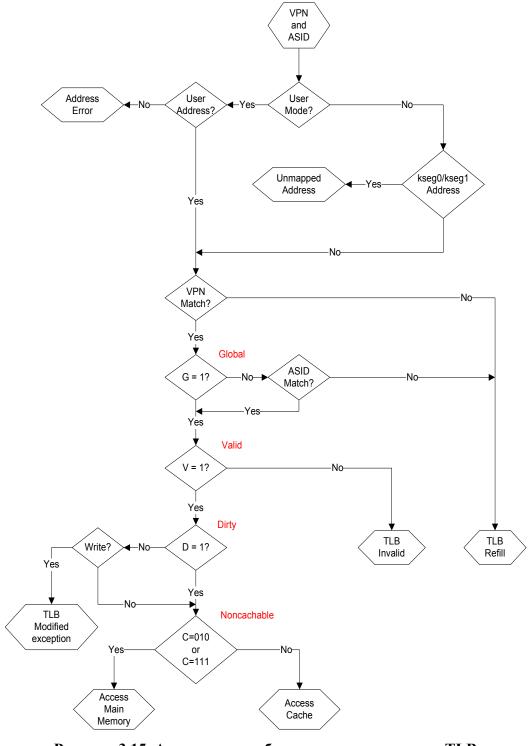

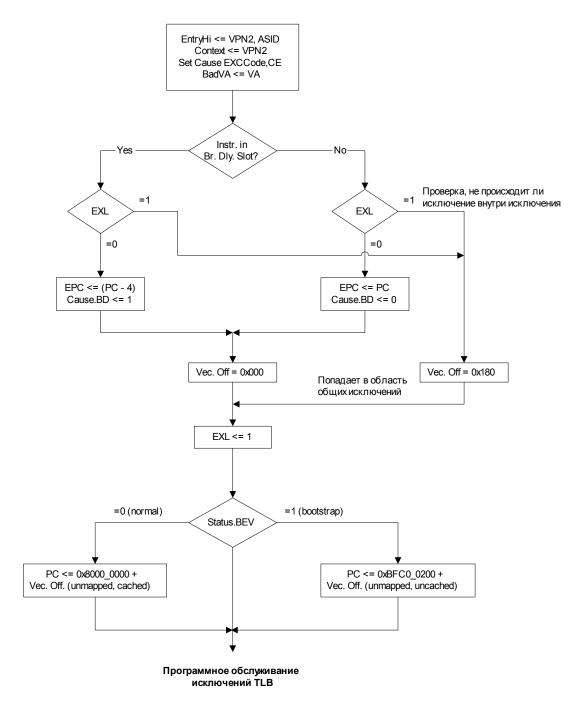

- среду разработки программ для СРU;